field-programmable gate array : ユーザが構成を設定できる集積回路。

以前も下記でとりあげました。

「FPGA & GPU/OpenCL」

http://decode.red/blog/20150913427/

このときはソフトウェアエンジニア目線でFPGAというものを見ていましたが、最近電子工作を始めるようになって、FPGAについてまた違った魅力を感じるようになりました。

そこで最近Altera MAX10ボードを購入したことから、AlteraのツールのModelSimを試してみました。

ここではFPGAプログラミングの初歩であるビットカウンタをツールのチュートリアルをもとにシミュレートしました。

環境 : ModelSim ALTERA STARTER EDITION 10.4b / Windows 10

tcounter.v

|

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 |

`timescale 1ns / 1ns module test_counter; reg clk, reset; wire [7:0] count; counter dut (count, clk, reset); initial // Clock generator begin clk = 0; forever #10 clk = !clk; end initial // Test stimulus begin reset = 0; #5 reset = 1; #4 reset = 0; #150 reset = 1; #4 reset = 0; end initial $monitor($stime,, reset,, clk,,, count); endmodule |

counter.v

|

1 2 3 4 5 6 7 8 9 10 11 12 13 14 |

`timescale 1ns / 1ns module counter (count, clk, reset); output [7:0] count; input clk, reset; reg [7:0] count; always @ (posedge clk or posedge reset) if (reset) count = 8'h00; else count <= count + 8'h01; endmodule |

[File]->[Change Directory]でソースがあるフォルダを選択します。

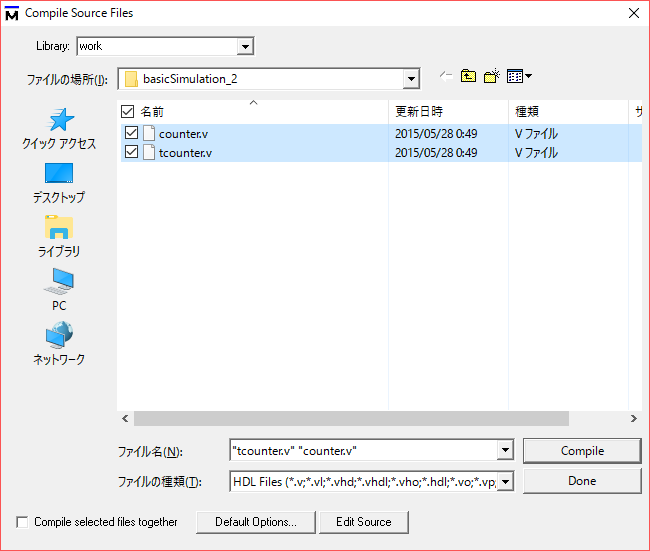

[Compile]->[Compile]を選択すると以下の画面がでてくるのでソースを選択します。

ソースと同じ階層に以下のようなcompileというファイルがあるので、自動的にworkフォルダが作成されるみたいです。

|

1 2 3 4 5 |

#!/bin/csh if (! -e work) then vlib work endif vlog counter.v tcounter.v |

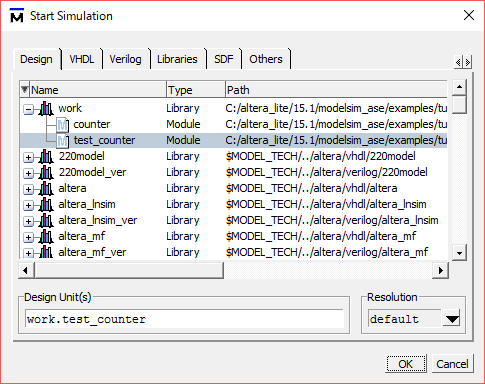

[Simulation]->[Start Simulation]でtest_counterを選択します。

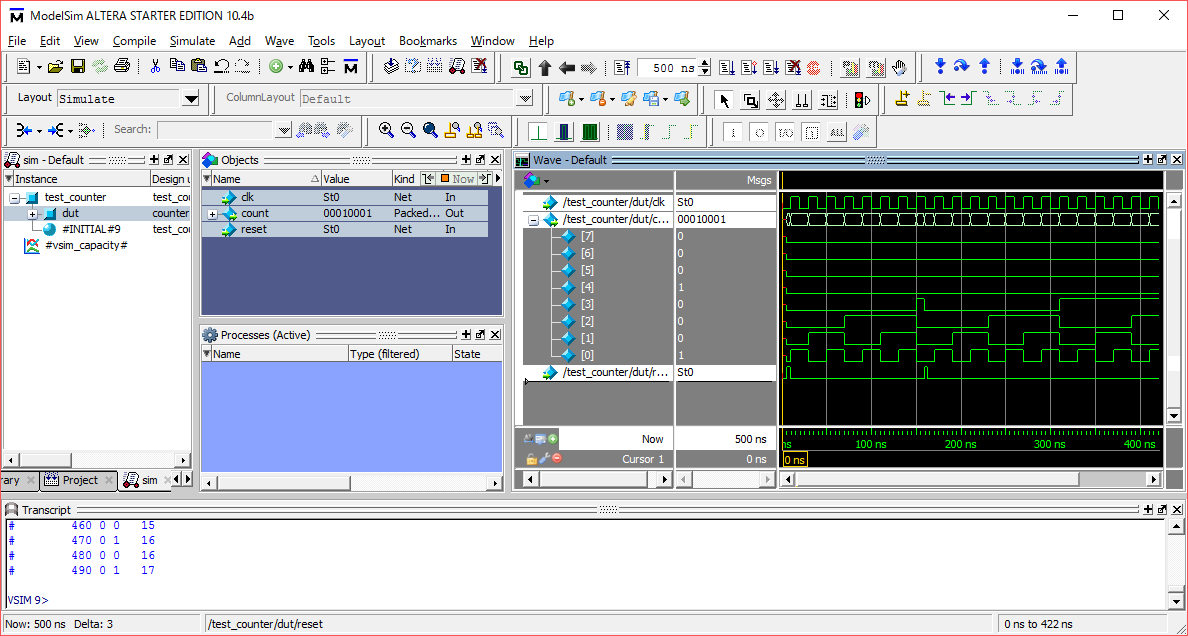

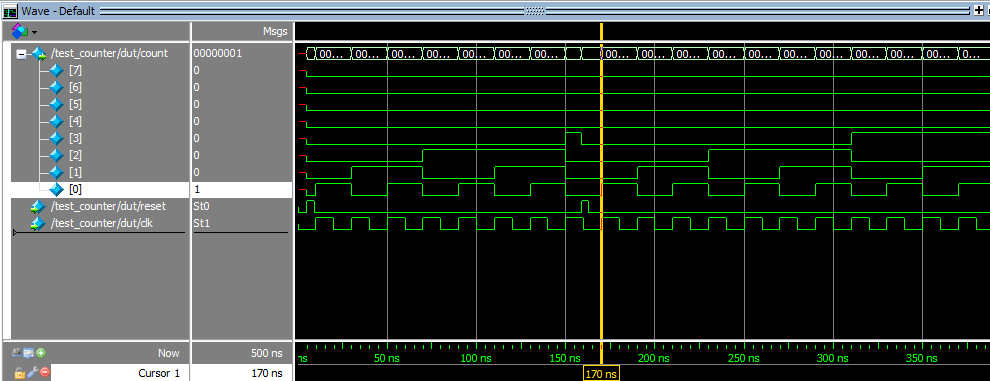

入力フォームRun Lengthを500nsにして、右のRunボタンを押すと、シミュレーション結果が表示されます。

テストではリセットでインクリメントされてきたカウントがリセットされて、また再開していることを確認できます。

FPGAではCPUも構成できます。つまりCPUを構成するのもデータ、そのCPUで走るプログラムもデータです。今回のテストのような単純なビットカウンタのようなものと区別しません。(Verilog-HDLでハードウェアを記述してデータを操作する)

最近いろいろと話題となっているFPGAが利用用途が広いのも納得できます。

またコンピュータの基本、デジタルであるということが、これだけいろんな技術が発達しても何も変わっていないことを再認識させられます。

今の目標としてはリアルタイムの画像データ処理で使えるようにしたいです。

またハードウェアに関して新しいブログもはじめました!